CPLD (Complex Programmable Logic Device) is composed of programmable interconnect matrix units around the center, of which the LMC logic structure is more complex, and has a complex I/O unit interconnect structure. Special circuit structures can be generated by users according to their needs to complete certain functions. Because fixed-length metal lines are used inside the CPLD to interconnect each logic block, the designed logic circuit has time predictability, avoiding the shortcoming of incomplete timing prediction of the segmented interconnect structure. By the 1990s, CPLDs developed more rapidly, not only with the characteristics of electrical erasure but also with advanced features such as edge scanning and online programmability. The more commonly used CPLDs from Xilinx and CPLDs from Altera.

CPLD Development History

In the 1970s, the earliest programmable logic device-PLD was born. Its output structure is a programmable logic macro unit because its hardware structure design can be completed by software (equivalent to manually designing a local indoor structure after the house is built), so its design is more flexible than pure hardware digital circuits, but their overly simple structure also allows them to implement only smaller circuits. In order to make up for the defect that PLD can only design small-scale circuits, in the mid-1980s, a complex programmable logic device-CPLD was introduced. At present, the application has been expanded to network, instrumentation, automotive electronics, CNC machine tools, aerospace measurement, control equipment, and so on.

CPLD Basic Structure

CPLD is the abbreviation for complex programable logic devices, and FPGA is the abbreviation of the field-programmable gate array. The functions of the two are basically the same, and the programming and other processes are basically the same (the programming files are different, but they are automatically generated by the software), but the internal implementation principle and structure of the chip are slightly different.

Programmable logic unit

The function is the same as the basic I/O port of FPGA, but the scope of application of CPLD is relatively limited, the performance and complexity of I/O are different from that of FPGA, and the supported I/O standards are less and the frequency is lower.

Basic logic unit

The basic logic unit in CPLD is the macro unit. The so-called macrocell is composed of some AND, or arrays plus flip-flops, in which the “AND-OR” array completes the combinational logic function, and the flip-flops are used to complete the sequential logic. Another important concept related to the basic logic unit of CPLD is the product term. The so-called product term is the output of the AND array in the macrocell, and its number indicates the CPLD capacity. The product term array is actually an “AND-OR” array. Each intersection is a programmable fuse. If it is turned on, it implements “AND” logic. There is usually an “OR” array after the “AND” array, which is used to complete the “or” relationship in the smallest logical expression.

Routing Pool, Routing Matrix

The wiring resources in CPLD are much simpler than those in FPGA, and the wiring resources are relatively limited. Generally, a centralized wiring pool structure is used. The so-called wiring pool is essentially a switch matrix, and the connection between the input and output items of different macrocells can be completed by tying nodes. Due to the lack of interconnection resources within the CPLD device, some difficulties will be encountered when the device is routed in some cases. Because the wiring pool structure of CPLD is fixed, the delay from the input pin to the output pin of CPLD is fixed, which is called Pin to Pin delay, expressed as Tpd. Tpd delay reflects the highest frequency that CPLD devices can achieve, and also it clearly shows the speed grade of the CPLD device.

CPLD basic structure examples

EPM7128S device

(1) Basic structure of EPM7128S device

EPM7128S device is mainly composed of logic array block LAB, macrocell, I/O control block, and programmable interconnection array PIA.

In a multi-array matrix structure, each macrocell has a programmable AND array and a fixed OR array, and a configurable flip-flop with an independently programmable clock, clock enables clear and set functions. Every 16 macrocells form a group to form a flexible logic array module LAB. Multiple LABs are connected to a global bus through a programmable interconnect array PIA. Each LAB is also connected to the corresponding I/O control block to provide direct input and output channels.

(2) EPM7128S macrocell structure

Each macrocell of the EPM7128S can be individually configured to work in combinational logic or sequential logic. A macrocell is mainly composed of the logic array, product item selection matrix, and programmable register. Programmable registers can be programmed to bypass according to logic needs to realize combinational logic. If it is used as a register, the corresponding programmable logic device development software will select an effective register working mode according to the design logic requirements, so as to minimize the device resources used in the design.

XCR3064XL device

(1) XCR3064XL device structure

The macrocell structure of the XCR3064XL device is composed of functional blocks and I/O units connected by a zero-power interconnection array, and each logic block contains 16 macrocells.

CPLD Architecture Diagram

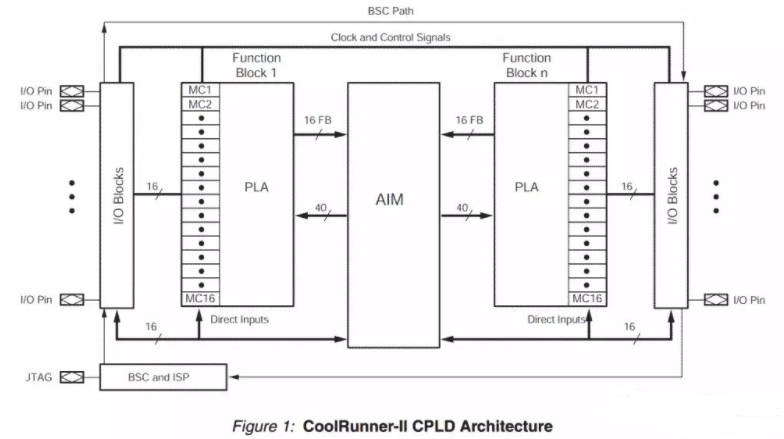

Take Xilinx CoolRunner-II as an example here. The following figure is the CPLD architecture diagram of Xilinx CoolRunner-II.

Now Easybom explains the content of the above picture for you.

1. This CPLD has a few functions blocks starting from “Function Block 1” to “Function Block n” (in the case of CoolRunner-II CPLD, this numbering range is 2 to 32)

2. 16 lines of output from each function block go into the AIM (Advanced Interconnect Matrix), while 40 lines of signals are input from the AIM to the function block.

3. Each function block has 16 MacroCells (MC1 to MC16).

4. Each MacroCell can access 16 signals from the I/O block.

5. The structure of the MacroCell is shown below. Each macrocell contains a product sum of flip-flops and PLA arrays that users can utilize to create combinatorial or sequential logic. So the maximum number of triggers available in CoolRunner-II CLPD (XC2C512) is 512! (Remember this number, we compare it to the number of flip-flops in the FPGA)

6. The AIM can be programmed to interconnect signals as needed. But as we saw in the second bullet point above, the number of signals per function block is limited.

Like PLA (Programmable Logic Array), the logic function of CPLD in each macrocell is electrically programmed through the System Programming (ISP) interface on JTAG. Once programmed, these flash-based connections have remained the same for years. This gives CPLDs the unique advantage of “instant-on” work. That is to say, the CPLD starts to work as soon as it is powered on because the program is burned in through the ISP flash memory.

To summarize, we can say that in a CPLD, there are several hundred functional blocks (or logic blocks), usually less than 1000, that can be accessed by a single large logic cell interconnect.

How to Use CPLD?

CPLD is a digital integrated circuit in which users construct logic functions according to their own needs. The basic design method is to use the integrated development software platform to generate the corresponding target file by means of a schematic diagram, hardware description language, etc., and transfer the code to the target chip through the download cable (“in-system” programming) to realize the designed digital system.

Here, take the responder as an example to talk about its design (decoration) process, that is, the design process of the chip. Most of the work of CPLD is done on the computer. Open the integrated development software (Max+pluxII of Altera Corporation) → draw the schematic diagram, write the hardware description language (VHDL, Verilog) → compile → give the input excitation signal of the logic circuit, carry out the simulation, check whether the logic output result is correct → carry out the pin Input and output lock (64 input and output pins of 7128 can be set as required) → generate code → transmit and store the code in the CPLD chip through the download cable. The pins of the 7128 chip have been drawn out. Connect the digital tube, the answer switch, the indicator light, and the buzzer to the chipboard through wires, and test the power. When the answer switch is pressed, the corresponding indicator light should be on, and the answer is correct. In the future, after the referee adds points, check whether the result of the digital display is correct. If there is any problem, you can re-revise the schematic diagram or hardware description language to improve the design. After the design is completed, such as mass production, other CPLD chips can be copied directly, that is, the code can be written. If you want to design other chips, such as traffic light design, you need to redraw the schematic diagram or write a hardware description language, repeat the above work process, and complete the design. This kind of modification design is equivalent to redecorating the house, and this kind of decoration can be carried out tens of thousands of times for CPLD.

Differences between CPLD and FPGA

1. Introduction to FPGA

FPGA (Field-Programmable Gate Array) is the product of further development on the basis of PAL, GAL, CPLD, and other programmable devices. It emerged as a semi-custom circuit in the field of application-specific integrated circuits (ASIC), which not only solved the shortcomings of the custom circuit but also overcome the shortcomings of the limited number of gate circuits of the original programmable device.

FPGA Features

1) Using FPGA to design an ASIC circuit (application-specific integrated circuit), users can get suitable chips without film production.

2) FPGA is one of the devices with the shortest design cycle, lowest development cost, and lowest risk in ASIC circuits.

3) FPGA adopts a high-speed CMOS process with low power consumption and is compatible with CMOS and TTL levels.

The FPGA is set up by the program stored in the on-chip RAM to set its working state. Therefore, the on-chip RAM needs to be programmed when working. Users can use different programming methods according to different configuration modes.

2. Introduction to CPLD

CPLD (Complex Programmable Logic Device) is composed of programmable interconnect matrix units around the center, of which the LMC logic structure is more complex, and has a complex I/O unit interconnect structure. Special circuit structures can be generated by users according to their needs to complete certain functions. Because fixed-length metal lines are used inside the CPLD to interconnect each logic block, the designed logic circuit has time predictability, avoiding the shortcoming of incomplete timing prediction of the segmented interconnect structure. By the 1990s, CPLDs developed more rapidly, not only with the characteristics of electrical erasure but also with advanced features such as edge scanning and online programmability. Xilinx CPLDs and Altera CPLDs are commonly used.

CPLD Features

It has the characteristics of flexible programming, high integration, short design and development cycle, wide application range, advanced development tools, low design and manufacturing costs, low requirements for designers’ hardware experience, no need to test standard products, strong confidentiality, and popular prices. Large-scale circuit design can be achieved, so it is widely used in product prototyping and product manufacturing (generally less than 10,000 pieces). CPLD devices can be used in almost all applications of small and medium-sized general-purpose digital integrated circuits. CPLD devices have become an indispensable part of electronic products, and their design and application have become a necessary skill for electronic engineers.

3. The differences between FPGA and CPLD

CPLD vs FPGA

①CPLD is more suitable for completing various algorithms and combinational logic, and FPGA is more suitable for completing sequential logic. In other words, FPGAs are more suitable for flip-flop-rich structures, while CPLDs are more suitable for flip-flop-limited and product-rich structures.

②The continuous wiring structure of CPLD determines that its timing delay is uniform and predictable, while the segmented wiring structure of FPGA determines the unpredictability of its delay.

③ FPGA has greater flexibility than CPLD in programming. CPLDs are programmed by modifying the logic function with fixed interconnected circuits, while FPGAs are programmed mainly by changing the wiring of the interconnections; FPGAs can be programmed under logic gates, while CPLDs are programmed under logic blocks.

④ The integration level of FPGA is higher than that of CPLD, and it has a more complex wiring structure and logic implementation.

⑤ CPLD is more convenient to use than FPGA. The programming of CPLD adopts E2PROM or FAST FLASH technology, no external memory chip is required, and it is easy to use. The programming information of the FPGA needs to be stored in the external memory, and the usage method is complicated.

⑥ CPLD is faster than FPGA and has greater time predictability. This is because FPGA is gate-level programming, and distributed interconnection is used between CLBs, while CPLD is logic block-level programming, and the interconnection between its logic blocks is lumped.

⑦In the programming method, CPLD is mainly based on E2PROM or FLASH memory programming, and the programming times can reach 10,000 times. The advantage is that the programming information is not lost when the system is powered off. CPLD can be divided into two categories: programming on the programmer and programming in the system. Most FPGAs are based on SRAM programming, and the programming information is lost when the system is powered off. Every time the system is powered on, the programming data needs to be rewritten into the SRAM from outside the device. The advantage is that it can be programmed any number of times and can be programmed quickly on the fly, enabling dynamic configuration at the board and system levels.

⑧CPLD has good confidentiality, while FPGA has poor confidentiality.

⑨ Under normal circumstances, the power consumption of CPLD is larger than that of FPGA, and the higher the integration, the more obvious it is. As the density of complex programmable logic devices (CPLDs) increases, digital device designers have the flexibility and ease of large-scale designs, and products can enter the market quickly. Many designers have found that CPLDs have the advantages of easy use, predictable timing, and high speed, however, in the past due to the constraints of CPLD density, they had to turn to FPGAs and ASICs. Designers can now realize the benefits of CPLDs with densities up to hundreds of thousands of gates.